Bu Yazımızda Neler Var:

What does the AI memory problem actually mean?

During training and inference, AI systems require massive amounts of weights, intermediate tensors, and continuous data flow. In this process, it is not only the question of “how much memory is available” that matters, but also “how fast can the system access that memory.” In classical architectures, processing and memory are separate, so data movement creates latency and turns into what is known as the von Neumann bottleneck. In short, the AI memory problem often stems not from insufficient computation, but from the inability to keep data in the right place at the right speed.

Why does moving data come with such a high cost?

As a model’s layers operate, they constantly need to fetch data from memory, and each fetch incurs both energy and time costs. A very fast processor alone does not solve the problem; if memory bandwidth remains low, processors sit idle and efficiency drops. That is why the industry has begun to prioritize moving less data as much as computing faster. This is exactly where next-generation hardware approaches aimed at solving the AI memory problem come into focus.

What does the next-generation chip approach promise?

The solutions coming to the fore aim to keep data closer to the processing units or to perform certain computations directly inside or next to memory. The in-memory computing approach seeks to perform specific operations near memory arrays instead of constantly moving data back and forth. This can provide both speed and energy advantages, especially for workloads like intensive matrix multiplication in neural networks. As a result, the AI memory problem shifts from simply “adding more RAM” to “rethinking the architecture itself.”

How does in-memory computing make a practical difference?

The goal of in-memory computing is to shorten the “journey” of data. When data moves less, latency decreases, energy consumption drops, and the same tasks are completed more efficiently. This approach can reduce costs in large-scale data centers while also improving battery life in edge devices. For this reason, in the AI hardware race, memory architecture has become a competitive field just as important as raw compute power.

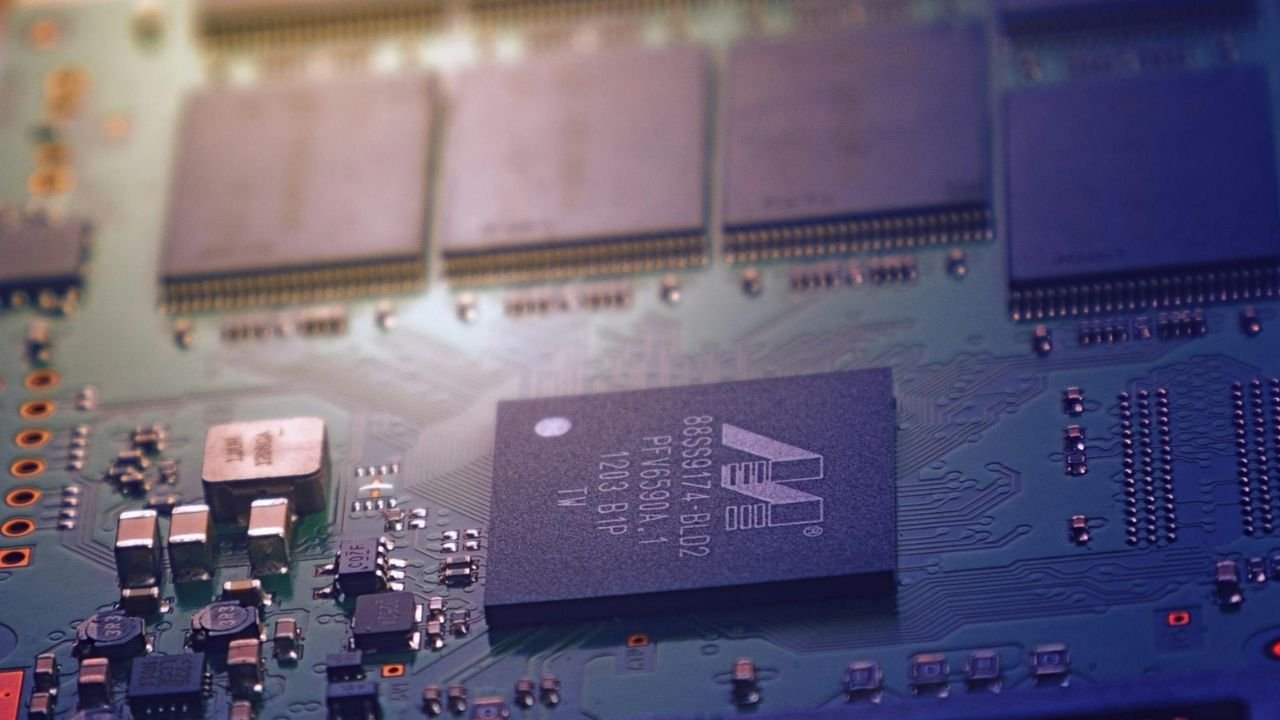

Why are memristor-based solutions drawing attention?

In recent years, memristor-based memory structures have been discussed more frequently in both academic circles and the R&D efforts of technology companies. The main reason is that they enable certain computations to be performed where the data is stored. Such an approach strengthens the link between storage and computation, offering an alternative and innovative path to address the AI memory problem. However, significant technical challenges—such as accuracy, suitability for mass production, and hardware stability—still need to be overcome before widespread adoption.

How do high-bandwidth memories change artificial intelligence?

Another strong approach is to “feed” the processor by dramatically increasing memory bandwidth through architectures like High Bandwidth Memory (HBM). With its very wide data paths and advanced packaging methods, HBM stands out especially in AI accelerators. This makes it easier to supply the data flow required by large models and improves overall system efficiency. In some scenarios, therefore, the AI memory problem can be alleviated not only by “bringing computation closer,” but also by “accessing memory faster.”

What does the market direction tell us?

As investments in artificial intelligence data centers grow, demand on the memory side is also increasing rapidly. Recent news indicates that demand for memory chips is putting pressure on production capacity and supply planning, and that AI-focused memory products are gaining importance. This picture shows that the AI memory problem is not just a technical issue, but also a strategic hardware topic that affects supply–demand balance.

What is the impact on everyday users?

Although these developments may seem relevant mainly to data centers at first glance, their effects can eventually reach consumers as well. More efficient chip architectures can allow AI features to run faster and with lower energy consumption on phones, computers, and home devices. Stronger memory architectures can also reduce the need to send every task to the cloud, enabling more on-device processing. This can make AI experiences more responsive while also offering certain advantages in terms of privacy.

What can be expected in the near future?

In the near term, rather than a single “miracle solution,” a hybrid era in which different architectures are used together for different workloads seems more likely. Some systems may rely on HBM to increase bandwidth, while others may focus on reducing data movement through in-memory computing approaches. Ultimately, the AI memory problem appears to be an issue that will be gradually alleviated not by software updates alone, but by the evolution of hardware design. The winner of this race will likely not be the architecture that computes the most, but the one that works most efficiently while moving the least data.

You Might Also Be Interested In: Why are Google Chrome extensions being talked about more in 2025?